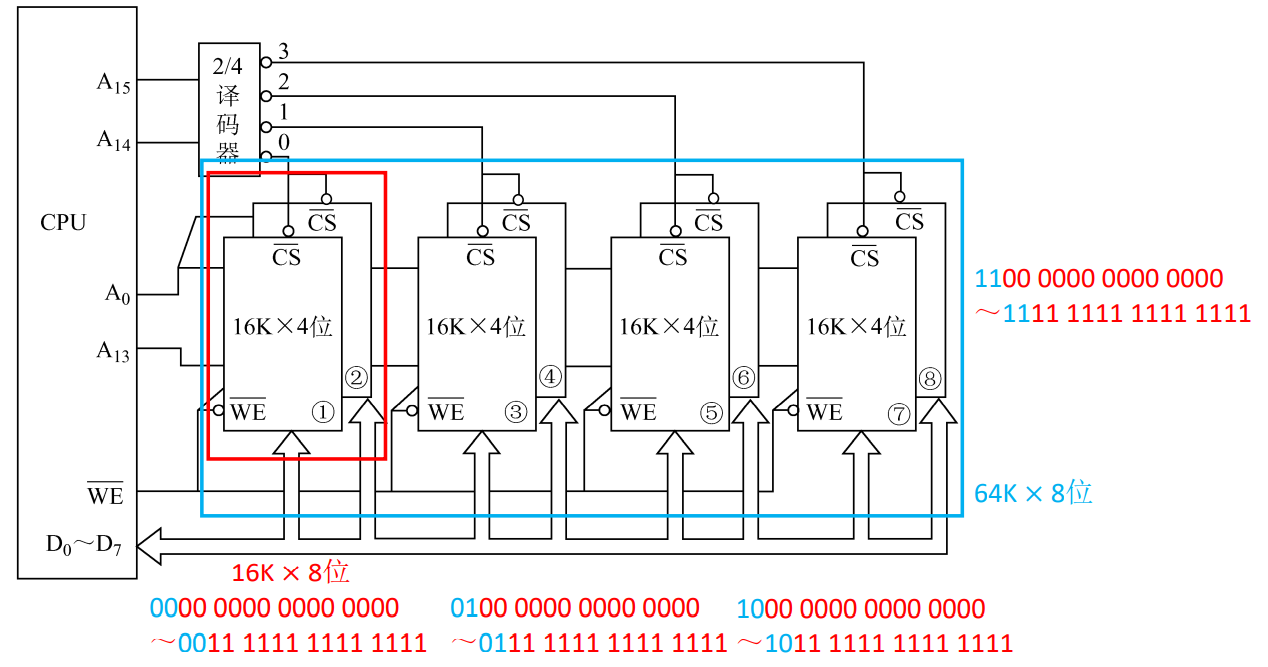

主存连接原理

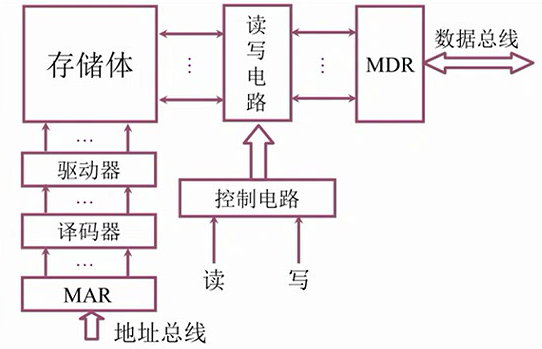

主存简单模型

三个输入信号:读/写信号、要读写的数据、数据的主存地址

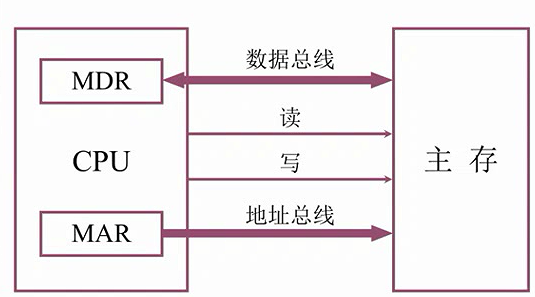

连接原理

三个总线:数据总线、地址总线、控制总线(读/写)

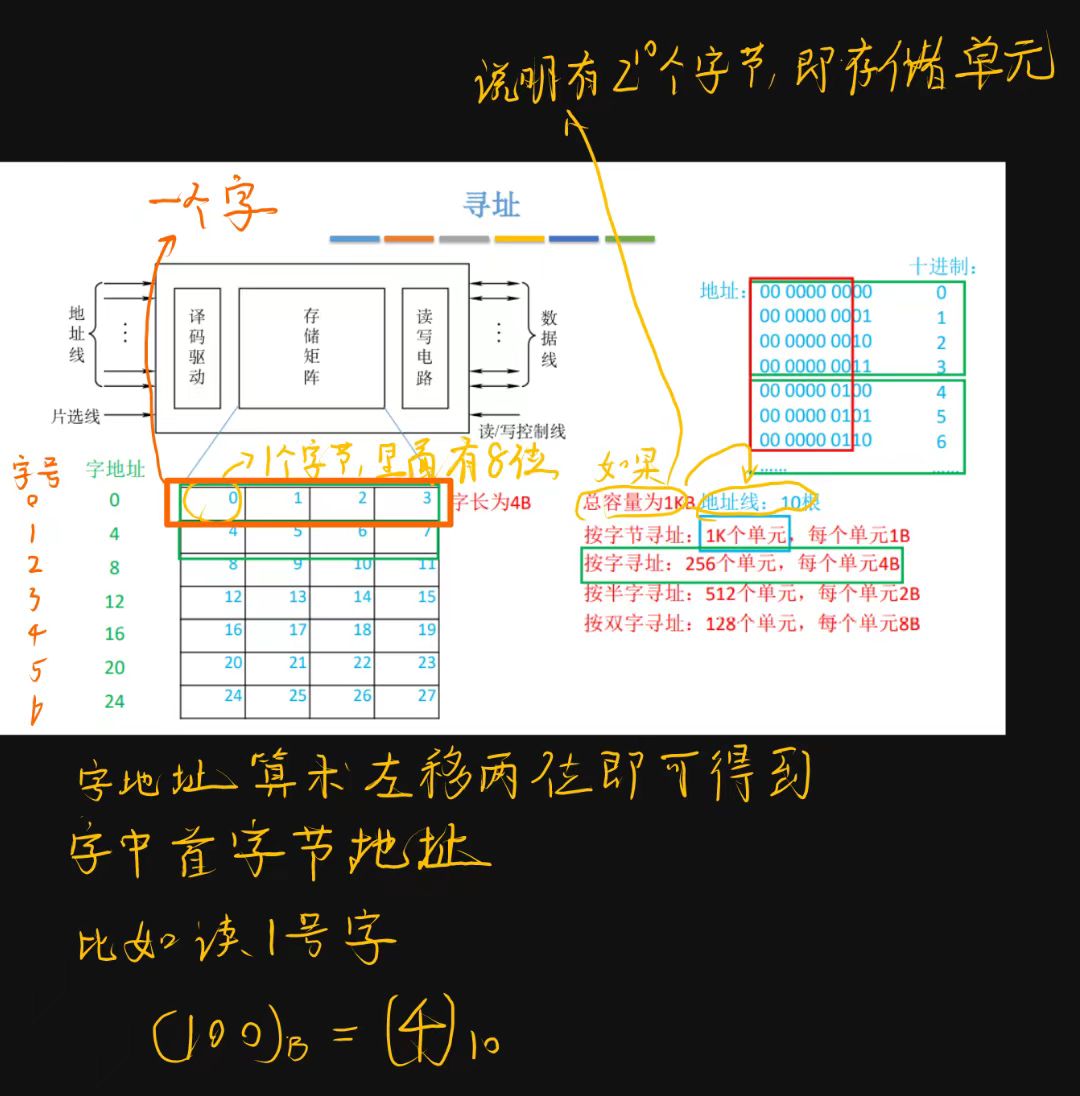

主存的地址单元分配

- 存储单元的数量:总容量 ÷ 每个单元的容量

- 地址线的数量应该等于总容量的位数。根据图中所示,1KB等于2的10次方字节(1KB = \(2^{10}\) B),因此有10根地址线。

- 如何存放一个字

- 字长为4B,实际上寻址时将四个存储单元看作一个

- 一组内有4个存储单元,后两位表示序号,前面表示所在组

- 每个存储单元存放两位十六进制数(8位二进制数)

- 共四个存储单元,也就是一个字

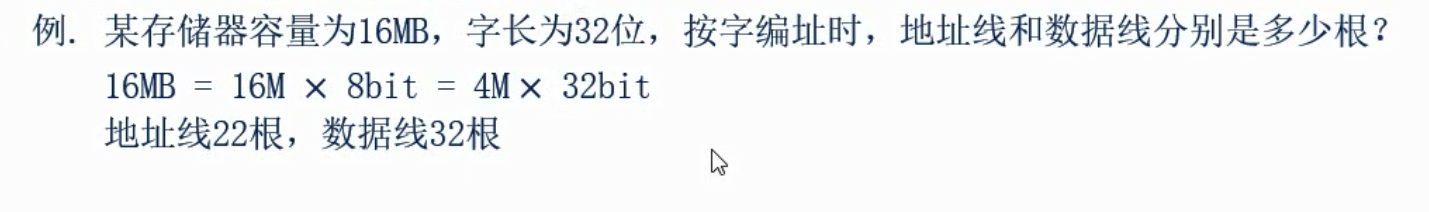

举例:

主存容量的扩展

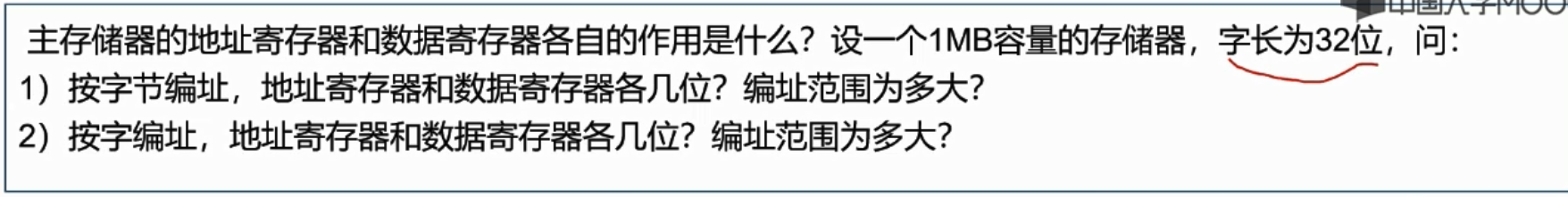

位扩展法

地址线、片选线和读写控制线并联

数据线依次连接CPU数据线的一位

如上图中就将8片\(8K * 1位\) 的储芯片扩展为了$8K $位

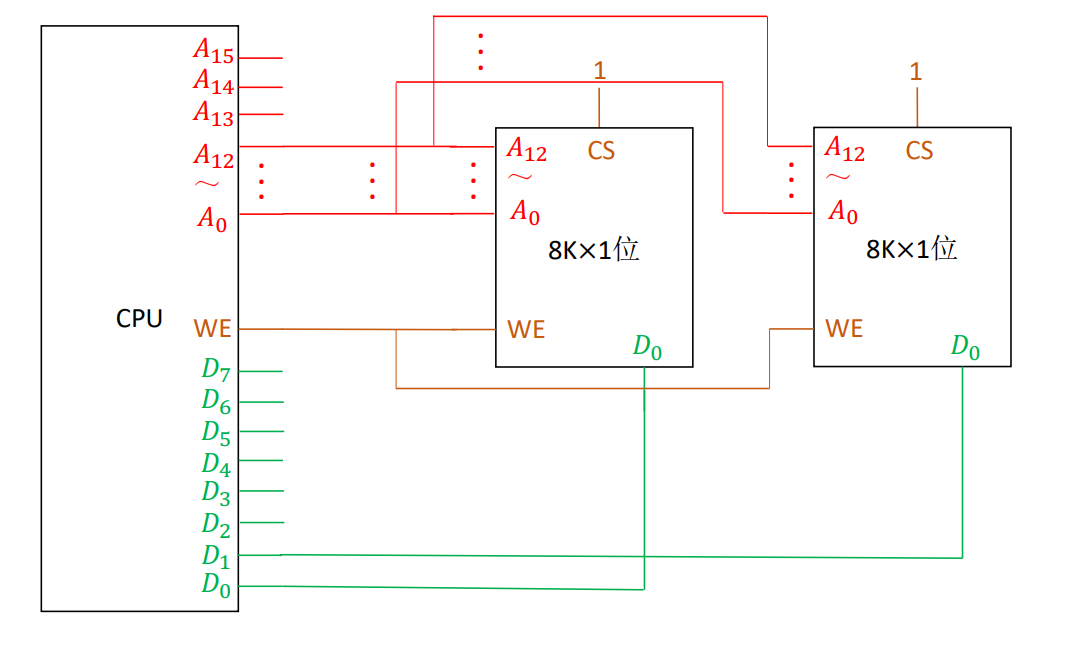

字扩展法

数据线、读写控制线和地址线并联

使用PU剩下的地址线连接片选线,选择当前读/写的芯片

线选法:直接将地址线与片选线连接,一根地址线对应一根片选线

译码器片选法:使用译码器将连接CPU地址线与片选线

| 线选法 | 译码器片选法 |

|---|---|

| n条线 → n个选片信号 | n条线 → \(2^n\)个选片信号 |

| 电路简单 | 电路复杂 |

| 地址空间不连续(形如11、00的信号是无效的) | 地址空间可连续可以增加逻辑设计 |

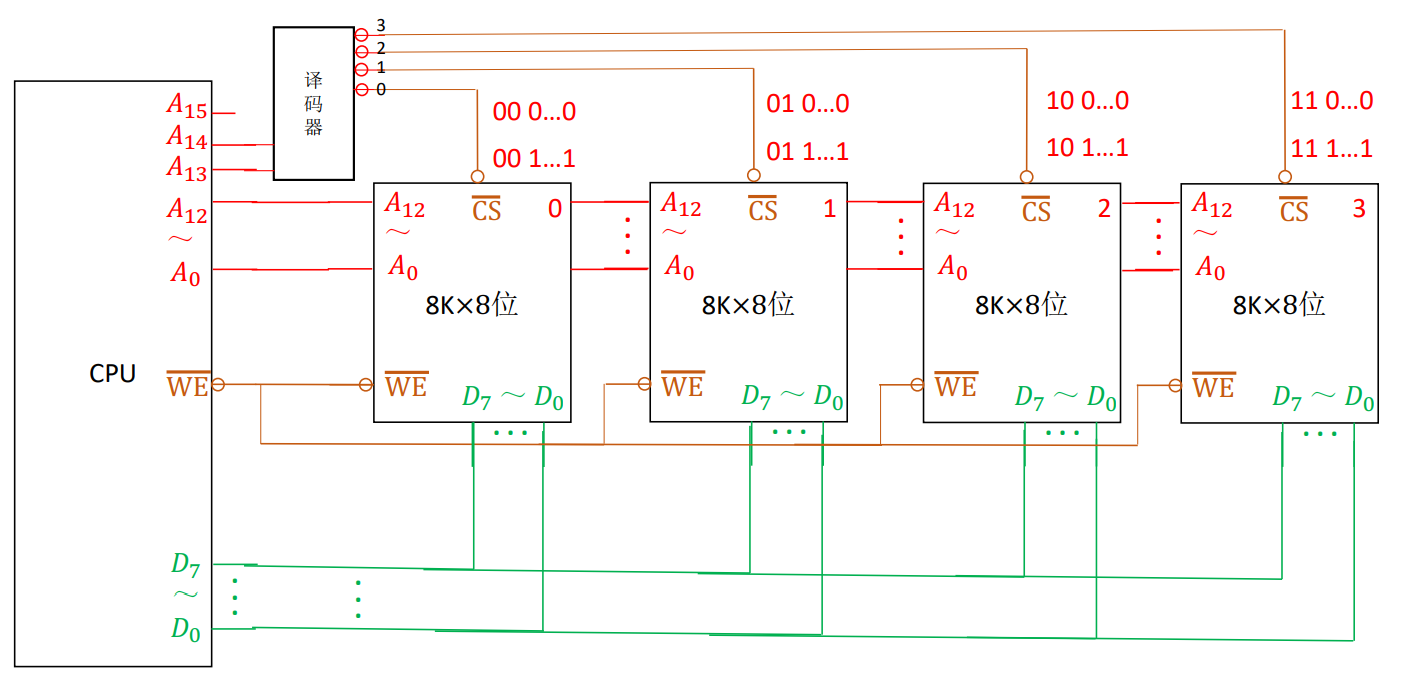

字位扩展

举例: