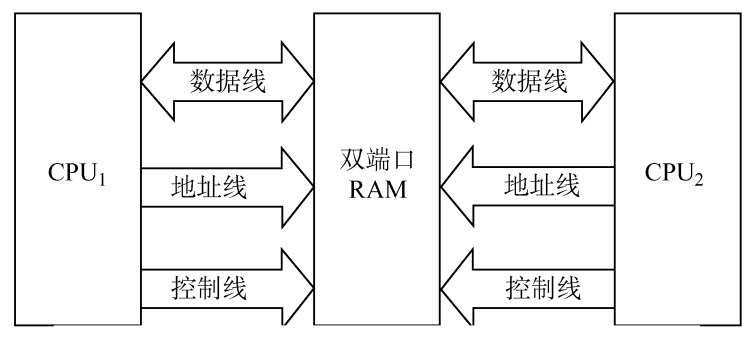

双端口RAM

拥有两个端口,可以同时访问不同的地址单元。

当连个端口访问同一个地址单元时:

- 两个端口不同时对同一地址单元存取数据 ✔

- 两个端口同时对同一地址单元读出数据 ✔

- 两个端口同时对同一地址单元写入数据 ❌

- 两个端口同时对同一地址单元,一个写入数据,另一个读出数据 ❌

可以通过忙信号解决这一问题,当有忙信号时,暂时关闭其中一个端口。

多模块存储器

单体多字存储器

- 每个存储单元内存储m个字

- 总线宽度为m个字

- 一次并行读/写m个字

优缺点

- 优点

- 提高了带宽,增加了读写速度

- 缺点

- 指令和数据在主存内必须是连续存放的

- 对转移指令、不连续操作数据效果不明显

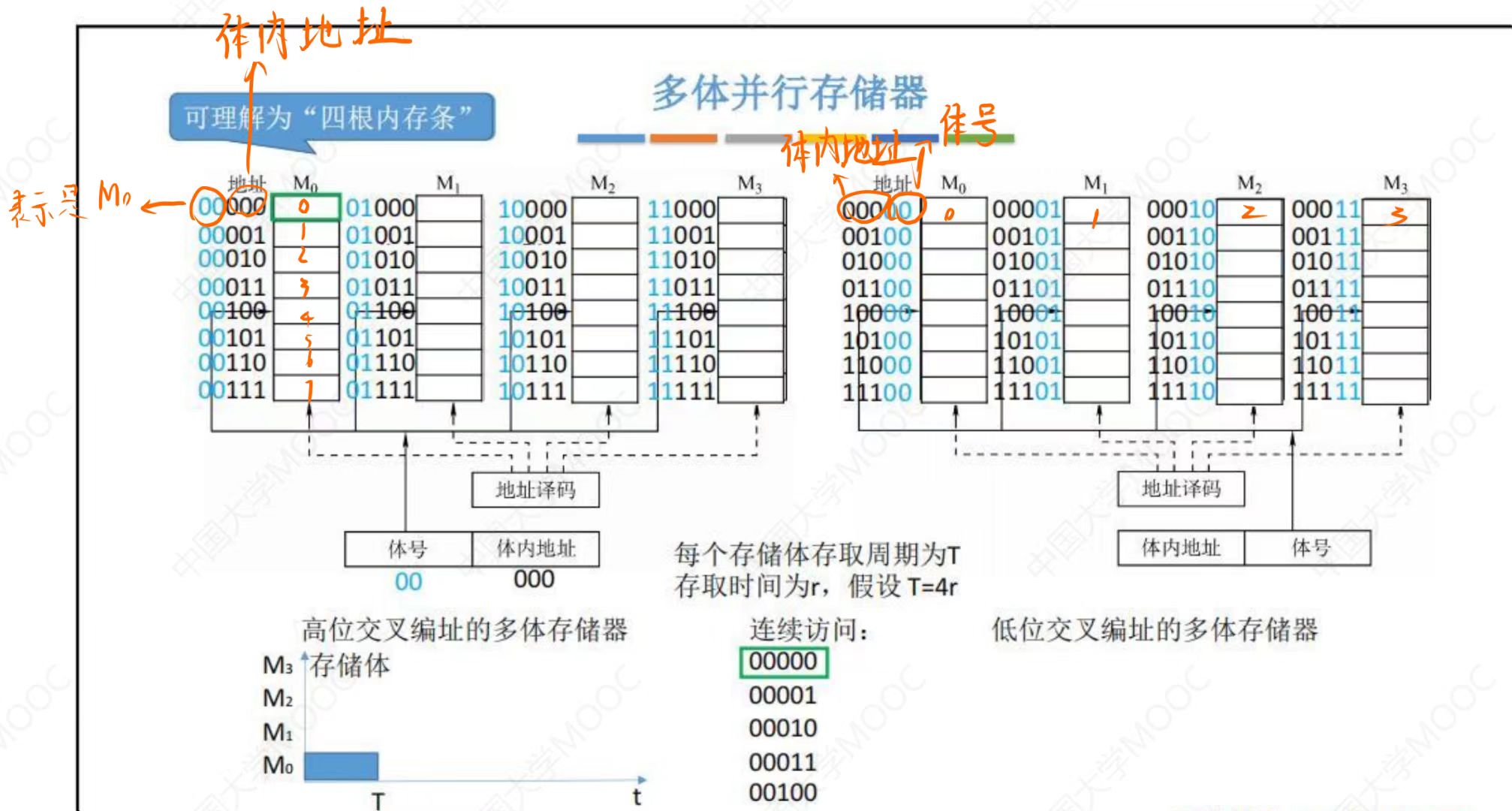

多体并行存储器

有多个存储模块,每个存储模块有相同的容量和存取速度;单独的读写控制器、地址寄存器和数据寄存器。

能并行工作,也能交叉工作

下面举例都是假设T = 4r, 其中r是存入时间,3r是恢复时间

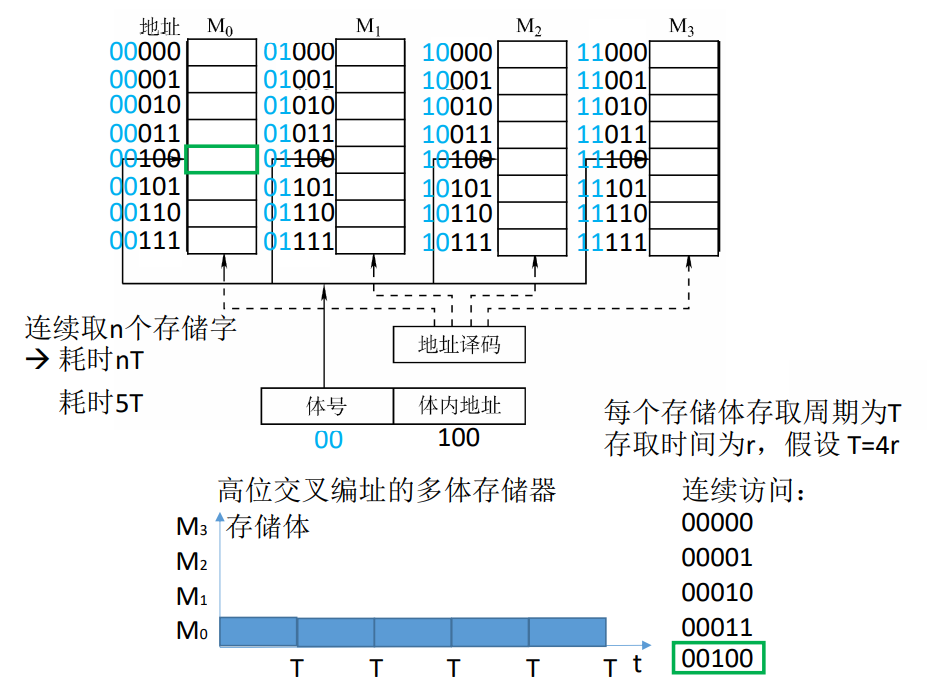

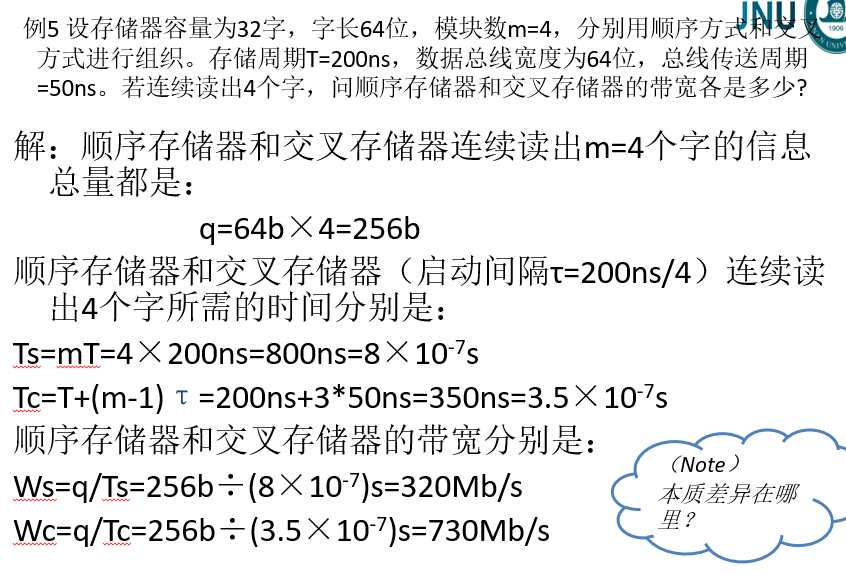

高位交叉编制(也称顺序存储)

编码中前2位作为区分是第几个存储体,后三位是体内偏移地址,从上往下0,1,2……7

连续访问时还是在一个模块内进行,实际上仅仅实现了扩容,不能提高访问速度。

高位交叉编制不满足程序的局部性原理。

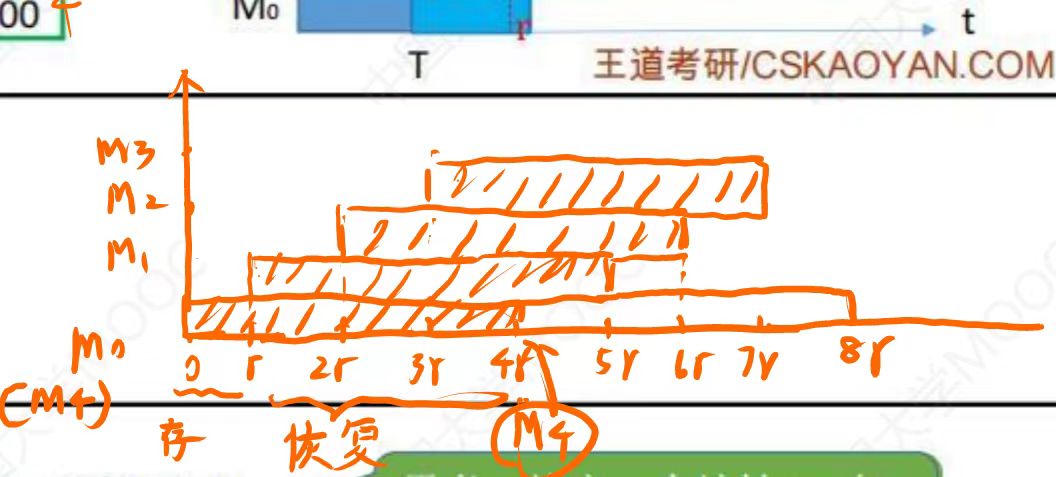

低位交叉编制(也称交叉存储)

后2位作为存储体编号,前3位作为体内偏移地址

当连续访问时,在多个模块间切换,提高了吞吐效率。

低位交叉编制满足程序的局部性原理。

举例:如何求带宽

例:模块数 ( m = 4 ),存储周期为 ( T ),字长 ( w ),数据总线宽度为 ( W ),总线传输周期为 ( r ),连续存储 ( n ) 个字,求交叉存储器的带宽。

连续存储 ( n ) 个字耗时: \(T + (n-1) \times (T + r)\) 前提: \(W \geq m \times r \times T\)

带宽: \(\frac{n \times W}{T + (n-1) \times (T + r)}\)

当 ( n ) 较大时,带宽趋近于: \(\frac{W}{r}\)

单个存储体的带宽: \(\frac{W}{T}\)