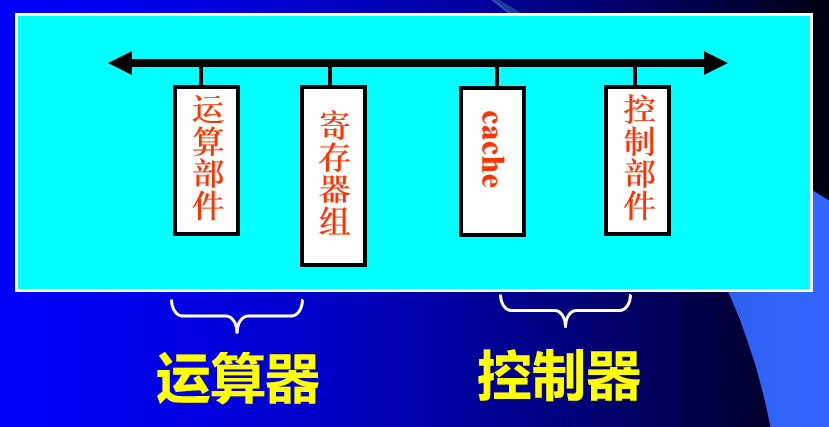

CPU的基本组成

寄存器组

寄存器:CPU在处理信息的过程中,用来暂时存放各种信息。

通用寄存器组

用户可通过编程访问的寄存器,在指令系统中为它们分配了相应的编号。指令中以寄存器号来指示。

暂存器

暂存器对编程者来说是透明的,即在程序中不会出现。

作用:暂时存放CPU处理过程中的临时信息,避免破坏通用寄存器的内容。

例如,实现从内存的单元A传送数据到另一个单元B。从单元A读出的数据先送到CPU中的一个暂存器,然后再从暂存器送入单元B。

指令寄存器IR

作用:用来存放当前正在执行的指令。控制器根据其内容(操作码以及地址信息)产生所需要的各种微命令。

程序计数器PC

作用:指示指令在存储器中的存放位置。

程序顺序执行时,每当从主存中取出一条指令后,PC内容就自动增量计数,指向下一条指令。

程序发生转移时,将转移地址送入PC,使其指向转移目的地的指令地址。

程序状态字寄存器PSW

作用:记录现行程序的运行状态和指示程序的工作方式。

特征位

进位位C、溢出位V、零值位Z、符号位S、奇偶位P等。

方式控制位

跟踪位T、中断允许位I、程序优先级字段、工作方式字段等。

地址寄存器MAR

作用:用来保存当前CPU所访问的数据cache存储器中单元的地址。

数据缓冲寄存器MDR

存放CPU与主存之间交换的数据。

由CPU写入主存的数据先送入MDR,主存地址译码找到指定单元后,再将数据从MDR送入到该单元。

从主存中读出的数据,先送入MDR,然后再送到指定的CPU内部某寄存器。

MAR和MDR是连接CPU与主存的桥梁,这两个寄存器不能编程访问,即对用户透明。

控制器

由程序计数器(PC)、指令寄存器(IR)、指令译码器、时序产生器和操作控制器组成,它是发布命令的“决策机

构”,即完成协调和指挥整个计算机系统的操作。

控制器的主要功能有:

1、从内存中取出一条指令,并指出下一条指令在内存中的位置。

2、对指令进行译码或测试,并产生相应的控制信号。

3、输出相应的控制信号,指挥并控制CPU,内存和I/O之间的数据流动的方向。

运算器

由算术逻辑单位(ALU)、累加寄存器(AC)、数据缓冲寄存器(DR)和状态条件寄存器(PSW)组成,它是数

据加工处理部件。 运算器所进行的全部操作都是由控制器发出的控制信号来指挥的,所以它是执行部件。

运算器的主要功能:

1、执行所有的算术运算。

2、执行所有的逻辑运算,并进行逻辑测试。