定义题

存储器的分类

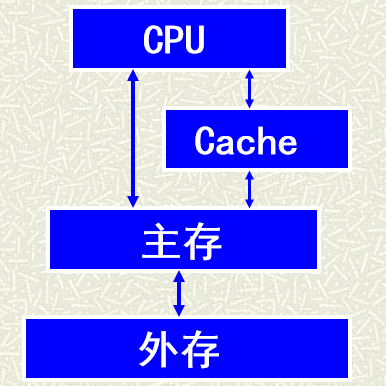

按在计算机中的作用分类

主存储器

辅助存储器(外存)

高速缓冲存储器(Cache)

几者的关系

按存储介质

半导体

- 利用双稳态触发器存储信息(动态存储器除外)

- 速度快,非破坏性读出(单管动态存储器除外)

- 信息易失(只读存储器除外)

- 作主存、高速缓存。

磁盘

- 利用磁层上不同方向的磁化区域表示信息。

- 容量大,非破坏性读出,长期保存信息,速度慢。

- 作外存。

光盘

- 利用光斑的有无表示信息。

- 容量很大,非破坏性读出,长期保存信息,速度慢。

- 作外存。

按存取方式分类

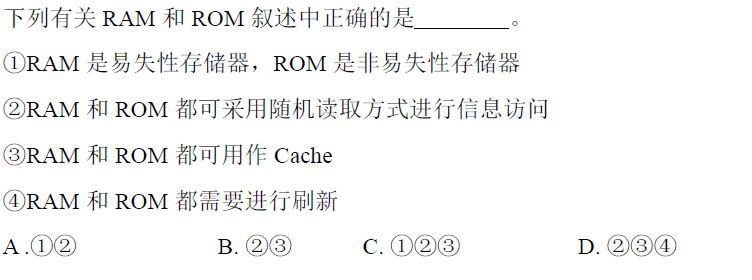

RAM(可读可写)

SRAM(静态)

- 依靠双稳态电路存储信息,不易失,不用刷新

- 速度快,做cache

DRAM(动态)

- 依靠电容存储,易失,需要频繁刷新

- 速度一般,作主存

ROM(只读不写)

固存

用户不能编程

PROM

用户可以一次编程

EPROM

用户可以多次编程,用紫外线擦除

EEPROM

用户可以多次编程,用电擦除

存储器分级存储

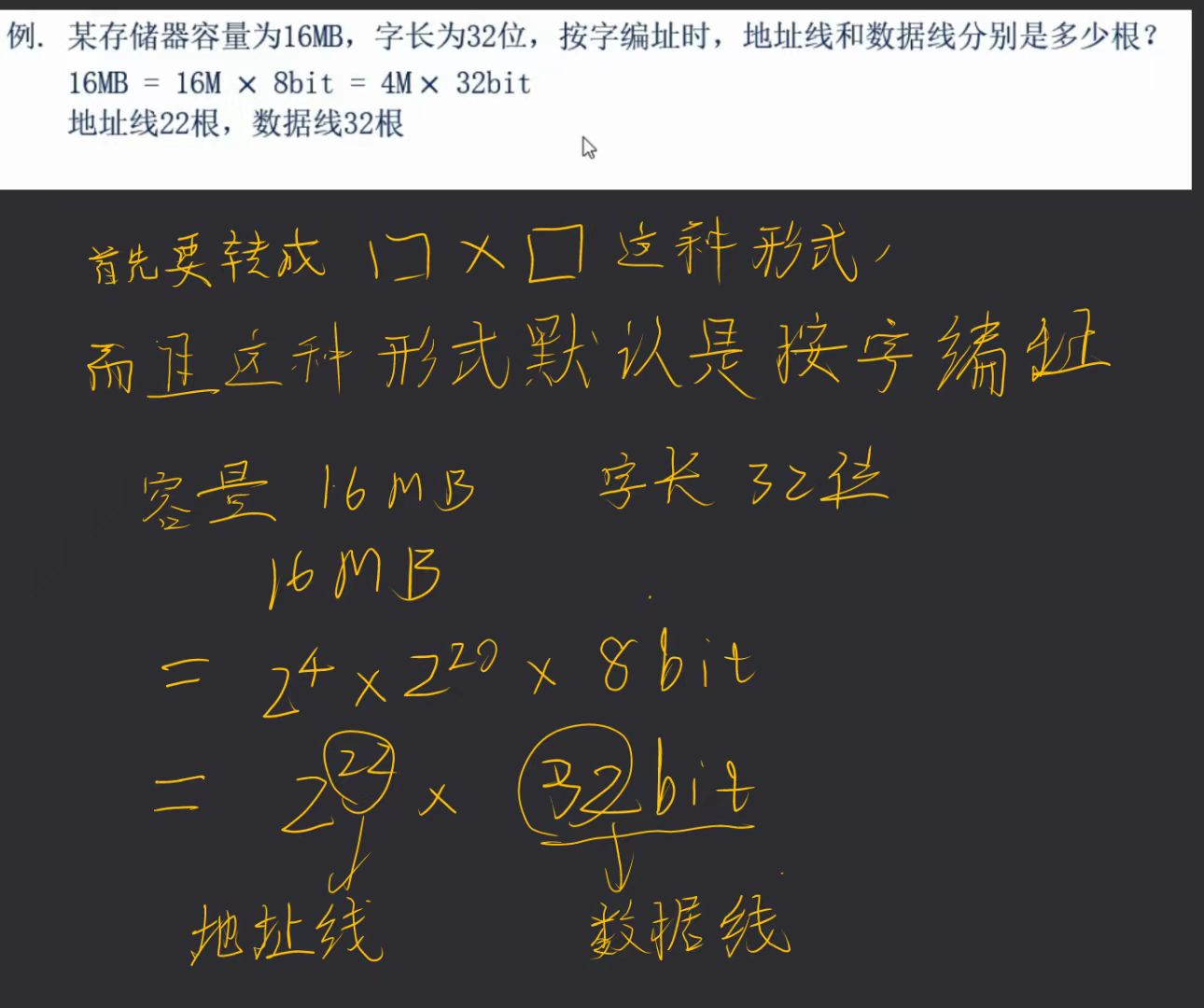

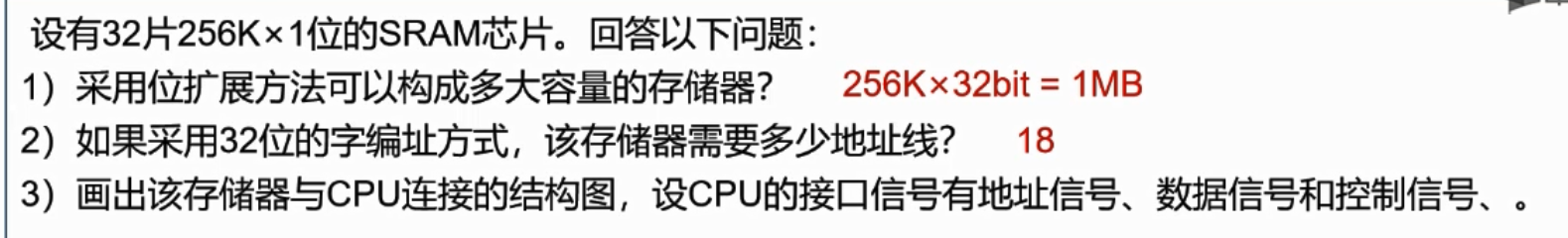

计算题

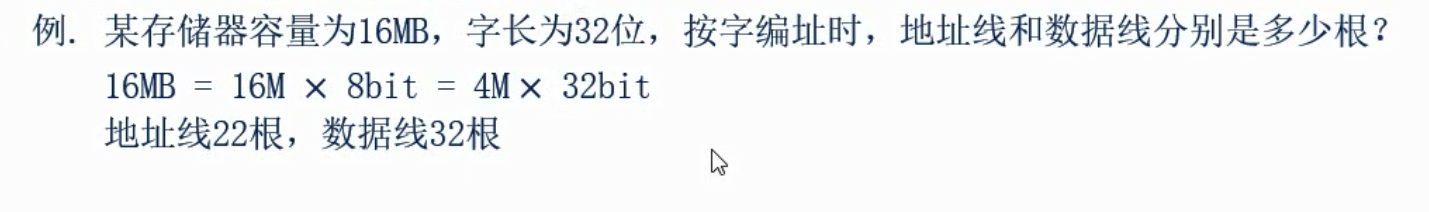

按字编址与按字节编址区别与计算

数据线与地址线的计算

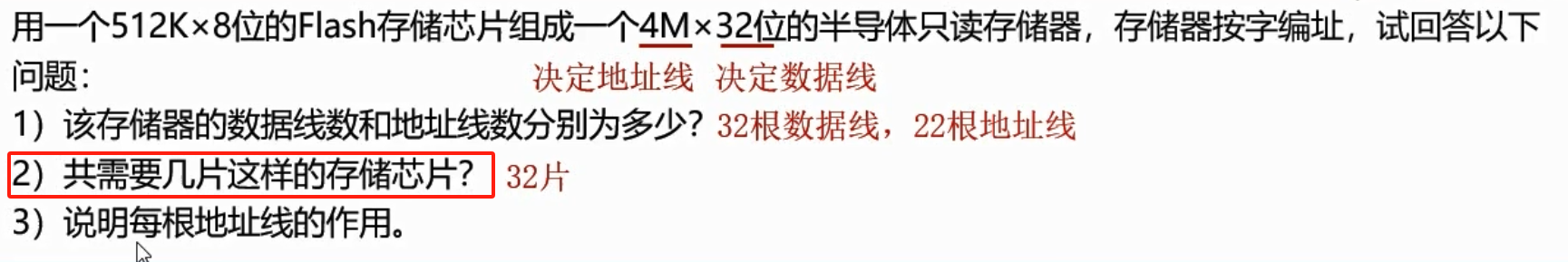

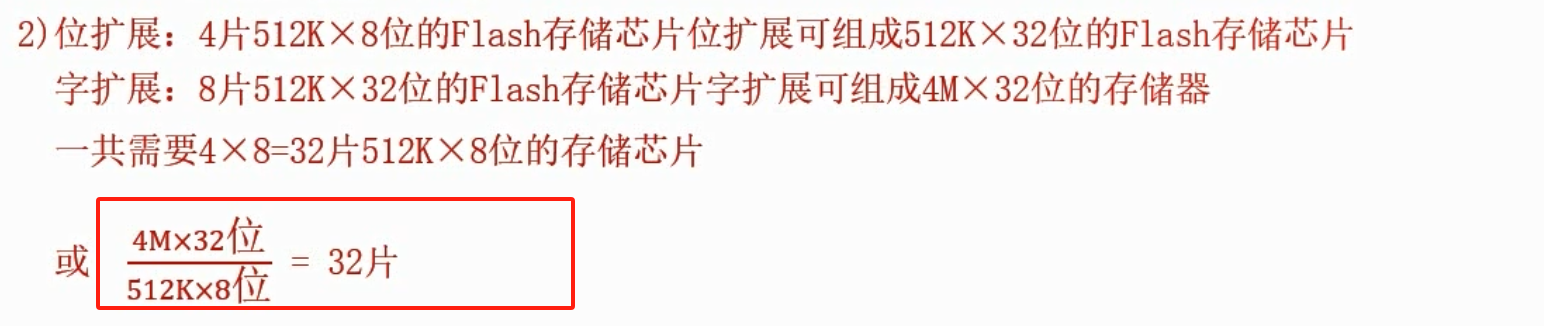

存储芯片数量的计算

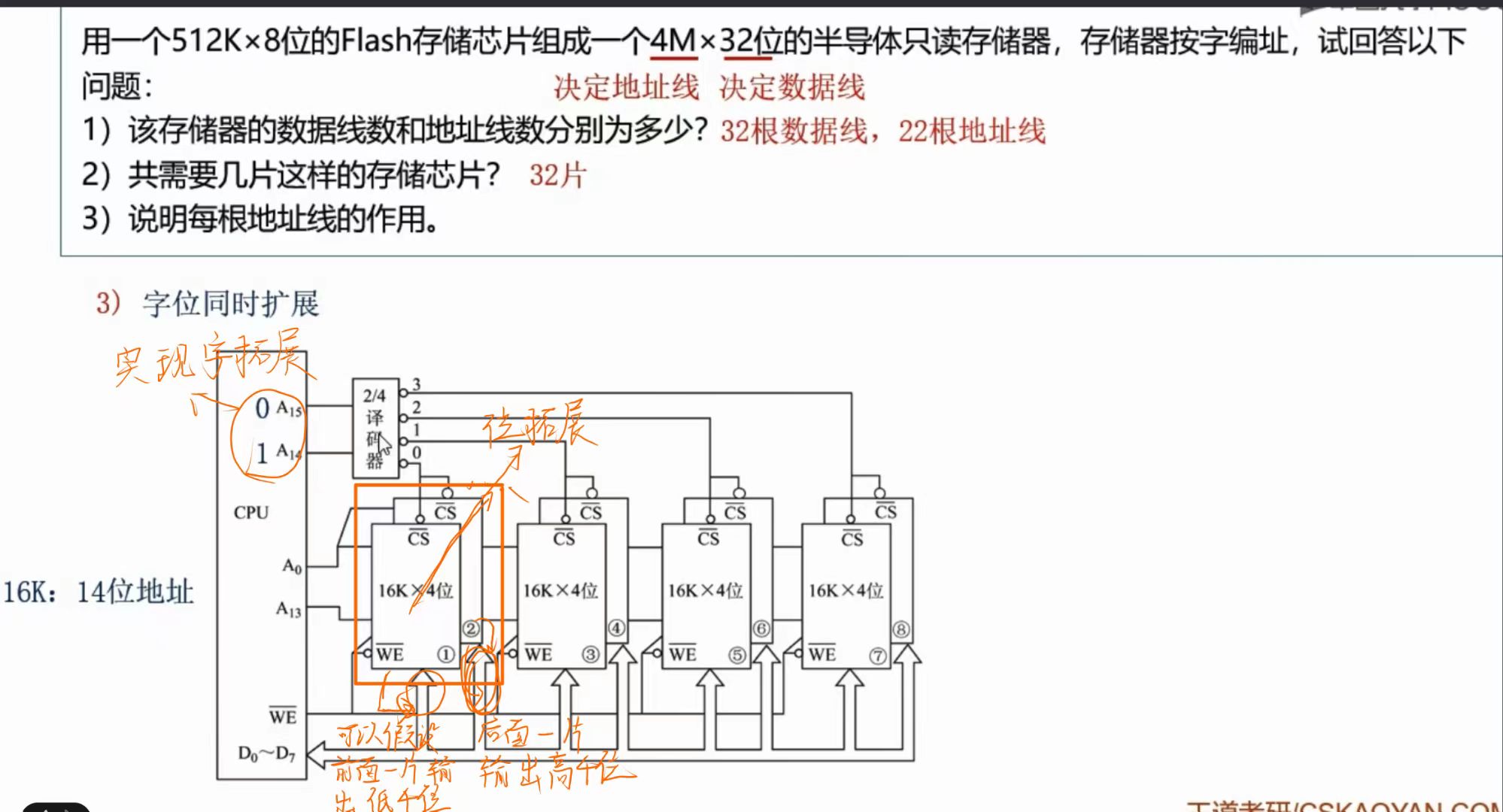

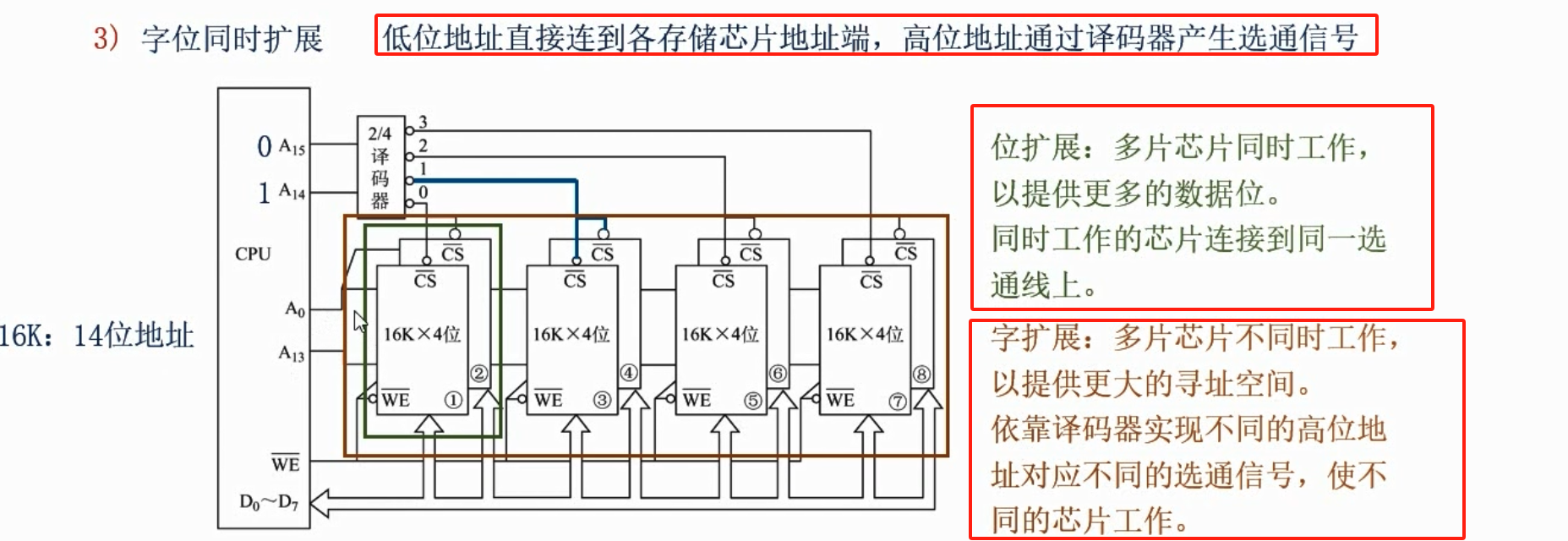

字拓展、位拓展中地址线作用分析

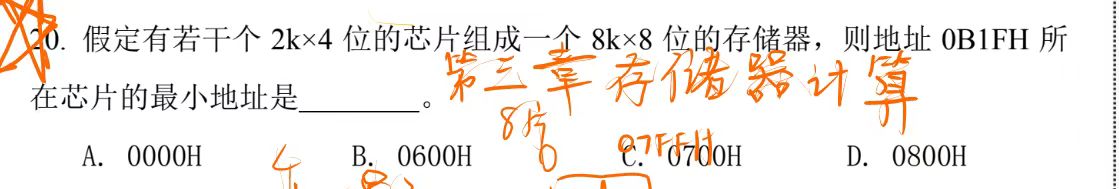

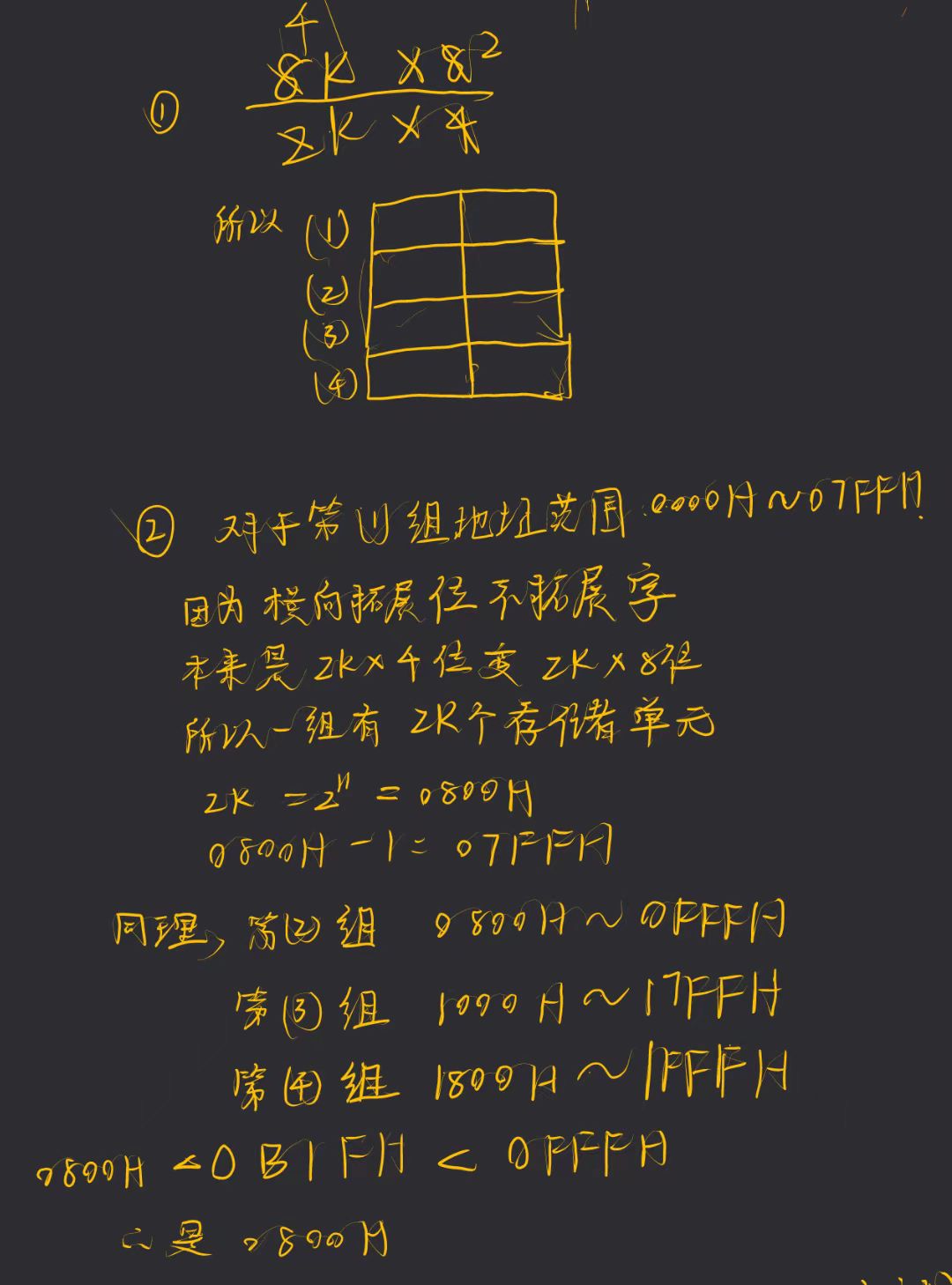

存储器字位拓展后芯片地址计算

方法1:

- 分析芯片字位拓展的组成

- 求每个/组芯片表示的地址范围

- 判断所给的地址落入了哪个地址范围

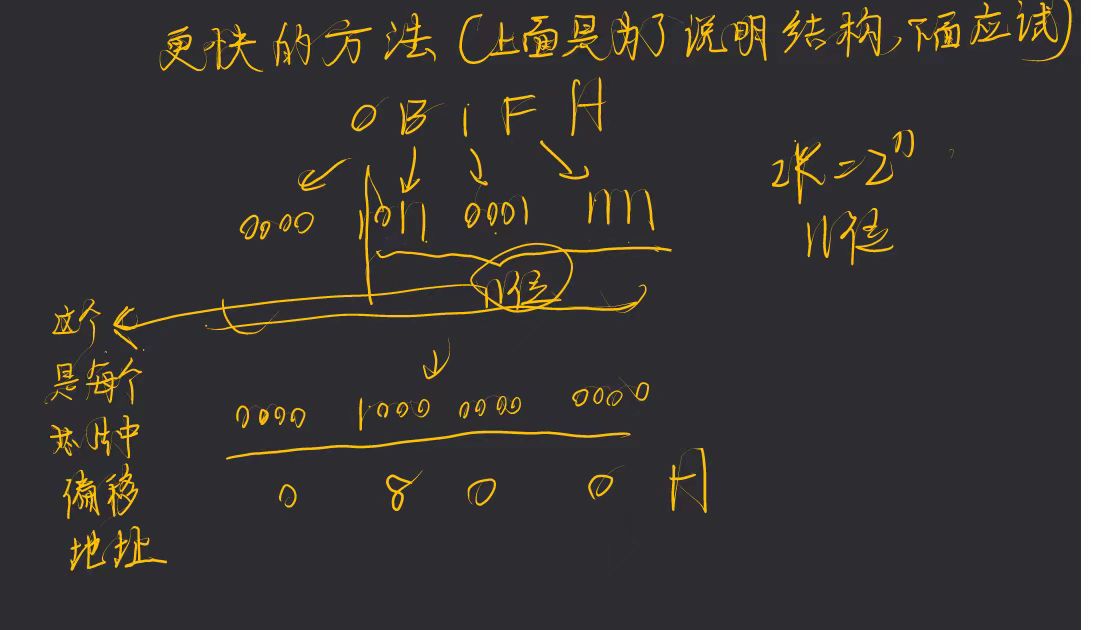

方法2:

将所给地址范围表示为二进制,将芯片原本大小所表示的偏移地址的位全部置0,再表示成十六进制

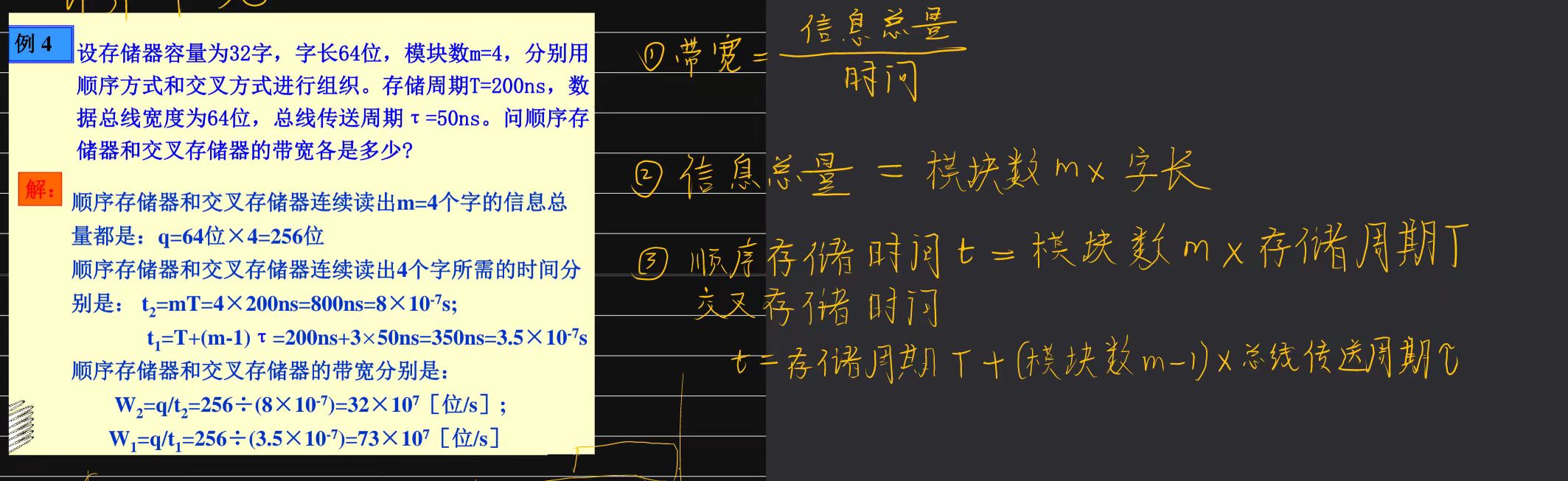

交叉与顺序存储器带宽的计算

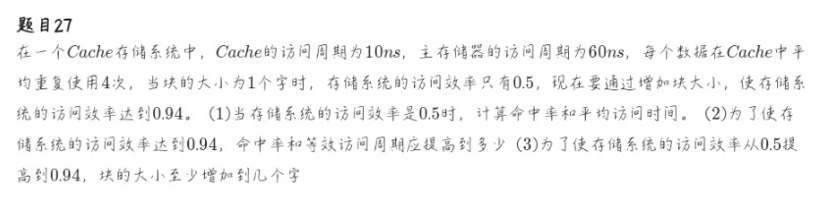

cache

cache效率的计算

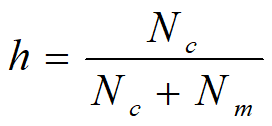

CACHE的命中率h

在一个程序执行期间,设Nc表示cache完成存取的总次数,Nm表示主存完成存取的总次数,h定义为命中率。则有:

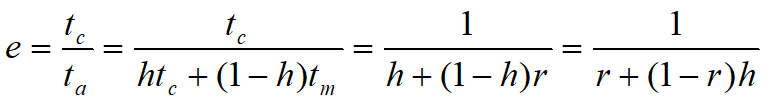

Cache/主存系统的平均访问时间ta

若tc表示命中时的Cache访问时间,tm表示未命中时的主存访问时间,1-h表示未命中率,则Cache/主存系统的平均访问时间ta为:

ta=htc+(1-h)tm

访问效率e

多级cache

某计算机的内存储器系统采用L1 cache、L2 cache和主存三级分层结构。访问第1级时命中率为95%,访问第

二级时命中率为50%,其余50%访问主存。假设访问L1 cache需要1个时钟周期T,访问L2 cache和主存分别

需要10T和100T,计算三级存储系统的平均访问时间Ta是多少周期?

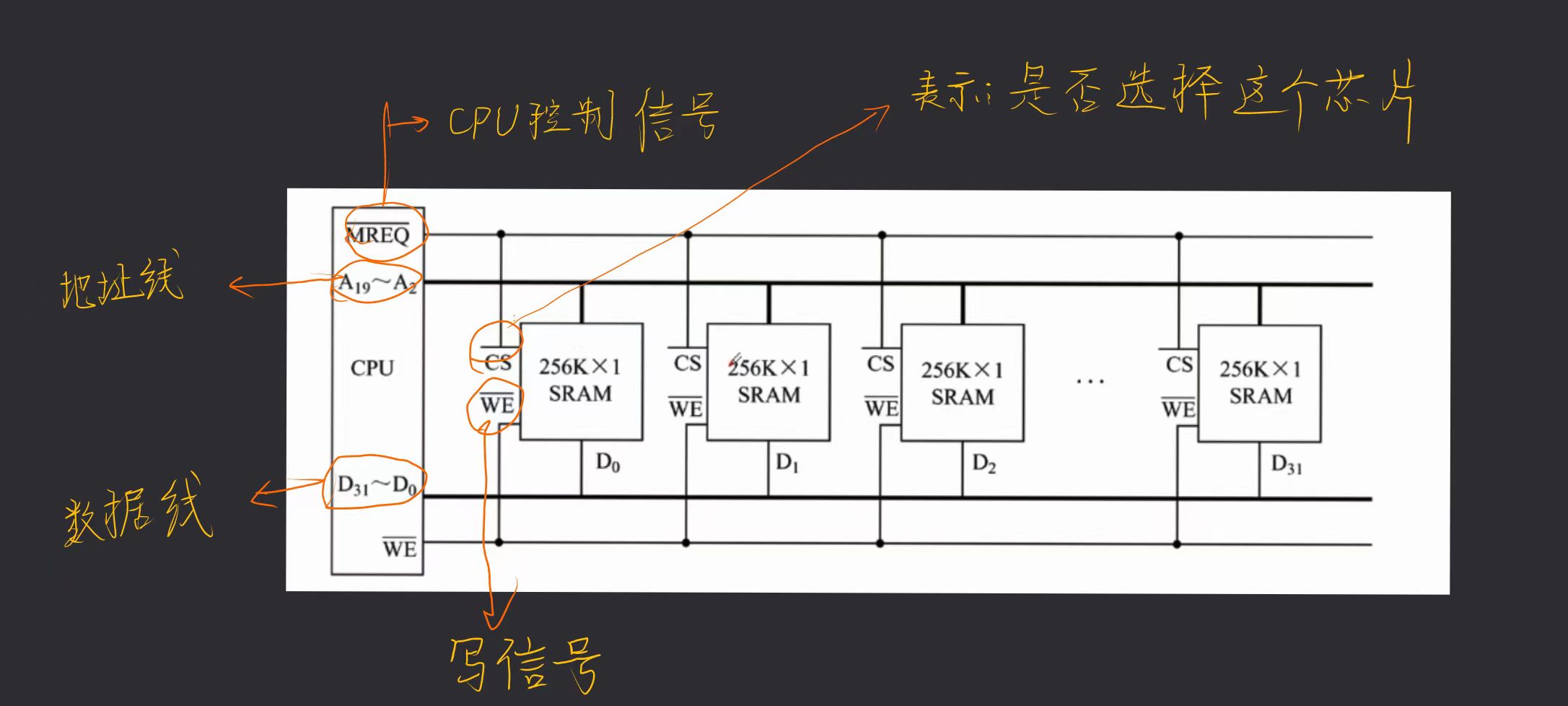

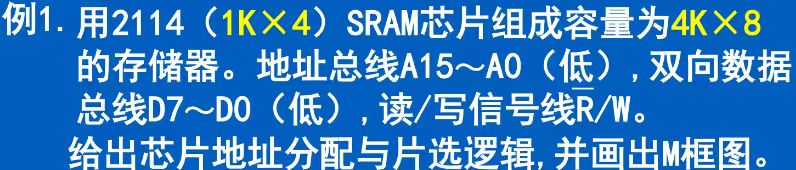

设计题

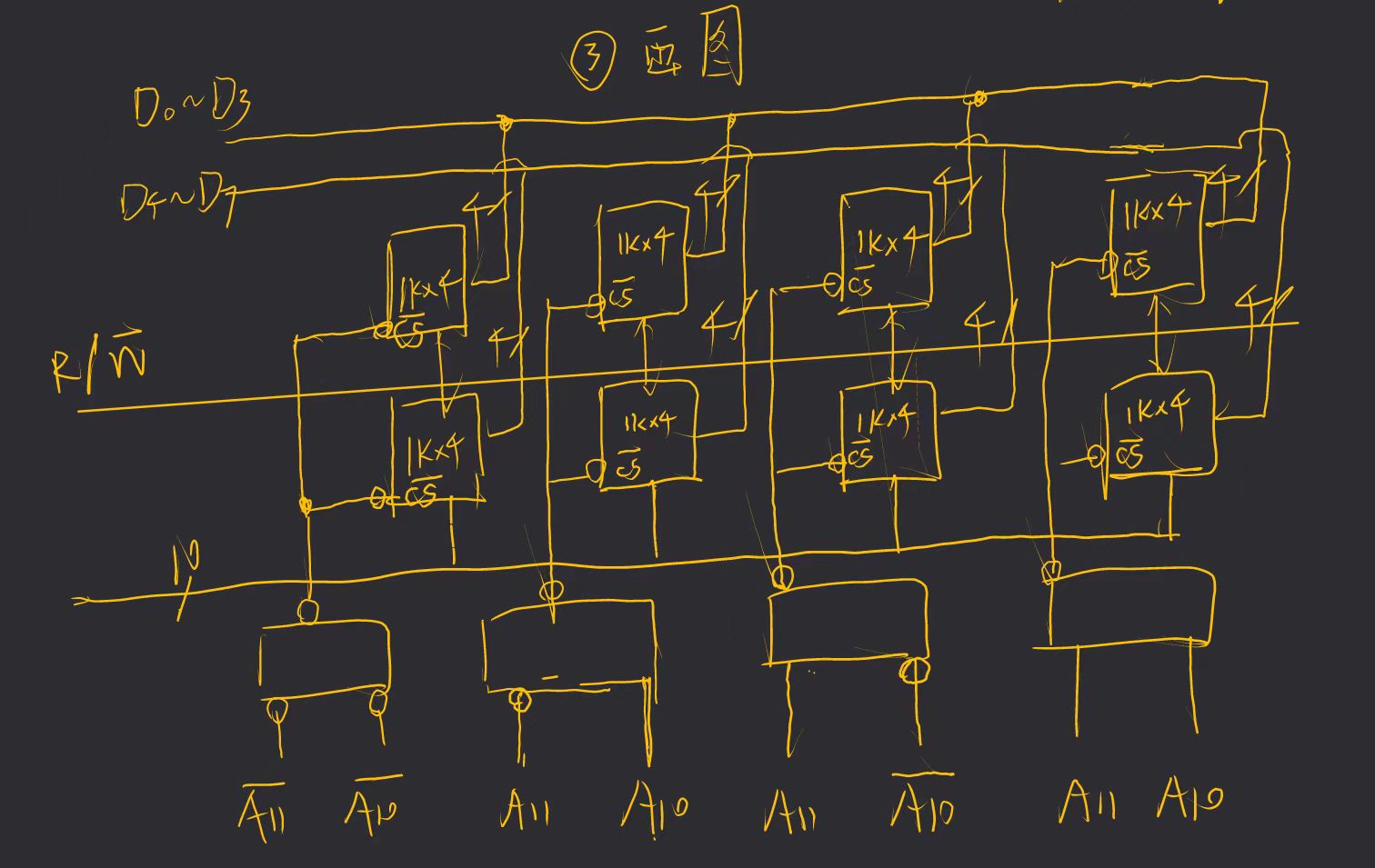

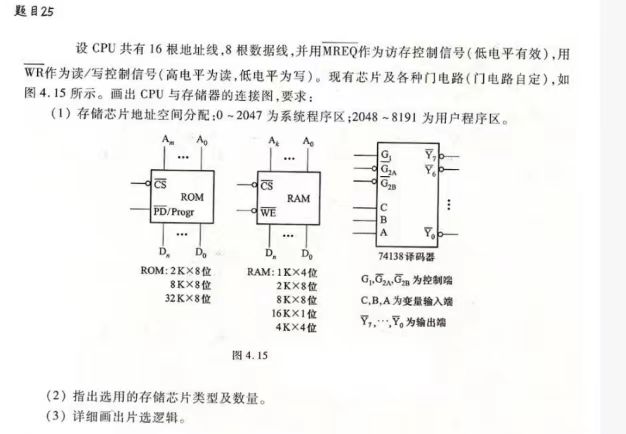

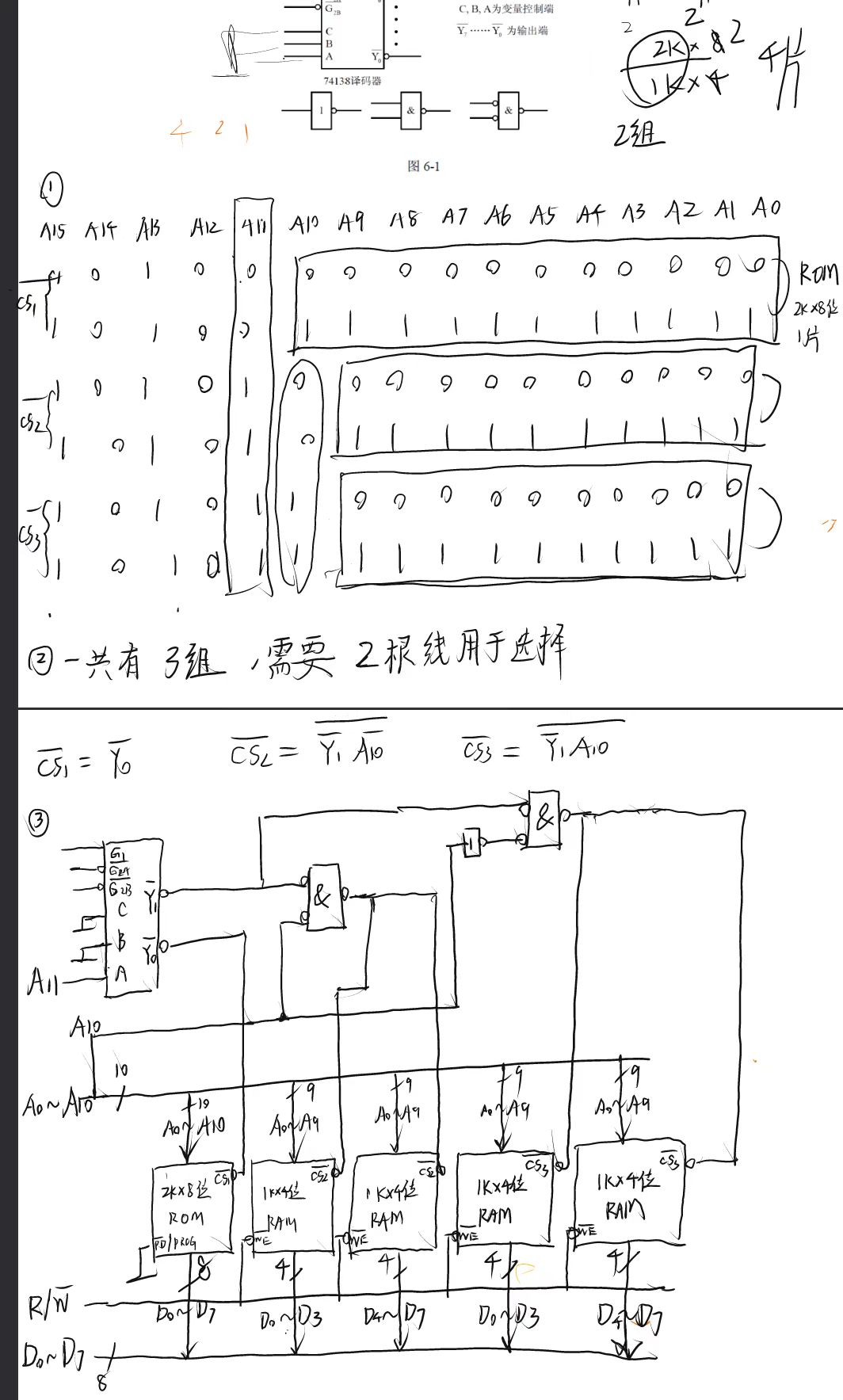

芯片设计,画存储器与CPU连接逻辑图

位拓展

字位扩展

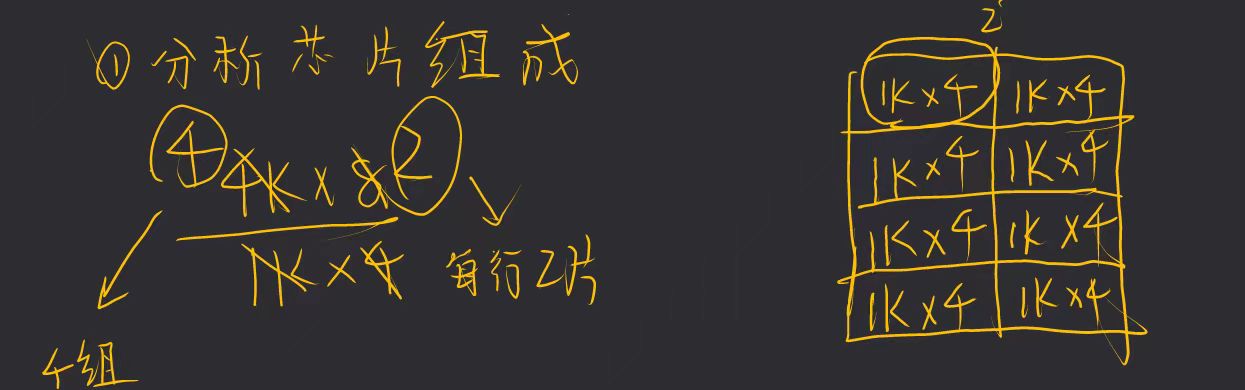

分析芯片组成

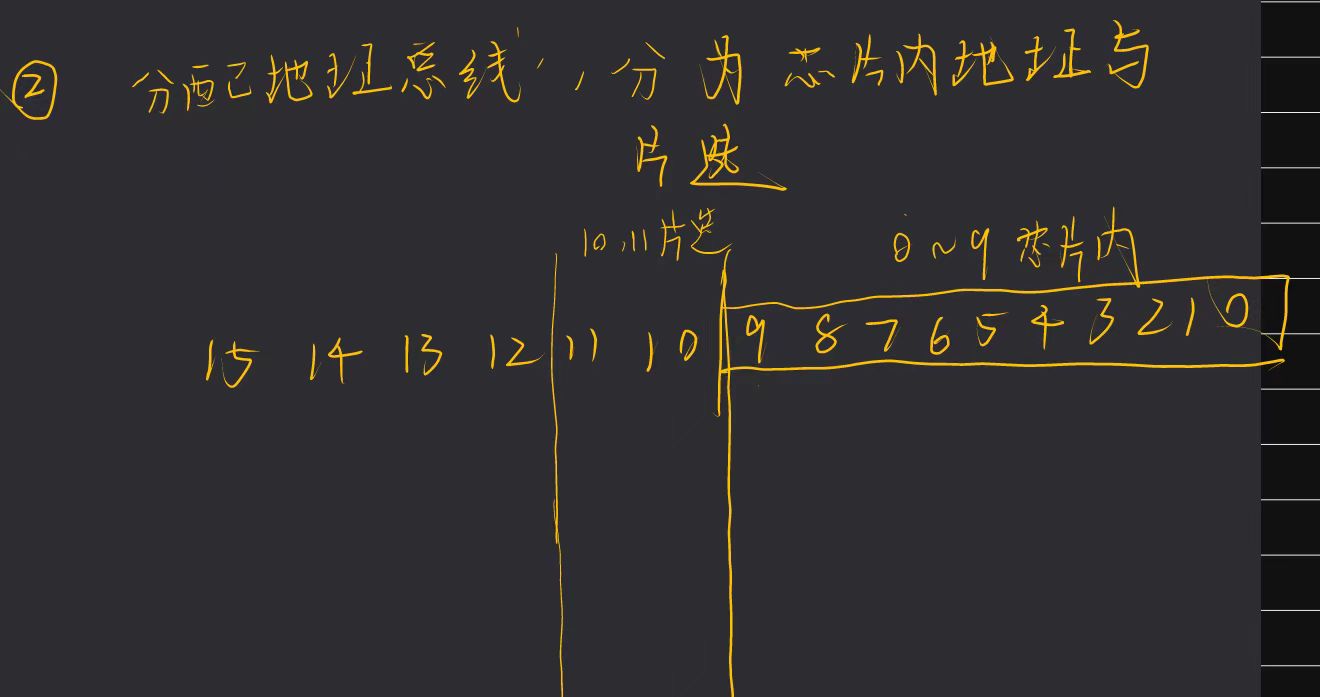

分配地址总线,分为芯片内地址与片选

画图

ROM,RAM选择

题目一

视频讲解:CPU设计与连线题型,需要进行RAM和ROM的选择,涉及系统程序区和用户程序区的理解

ROM对应系统程序区,因为read only表示不可被修改,RAM对应用户程序区,因为random access表示可以修改

先列“真值表”,列完后选择芯片。

比如一块芯片大小是2K,就是\(2^{11}\),就需要11位,片内偏移地址从\(A_{10}\)到\(A_{0}\)

芯片标准是先位拓展,不行再字拓展,然后根据所选择芯片划分片内偏移地址范围,再根据芯片数量选择需要多少根地址线作为片选信号

画数据线和地址线可以画集数线,标注数量就行,画每个芯片连接到集数线需要标注数量和对应范围

题目二

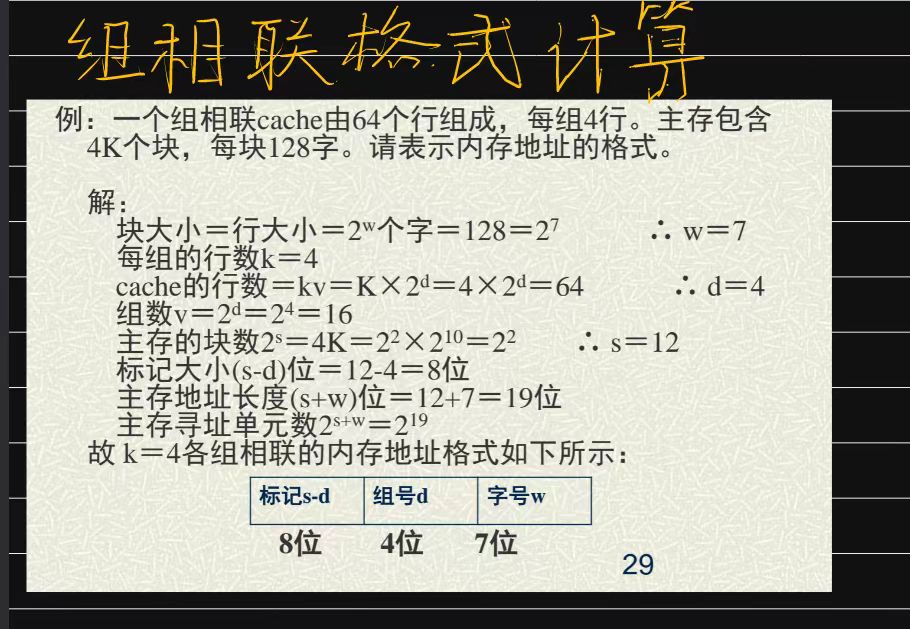

cache和主存的映射

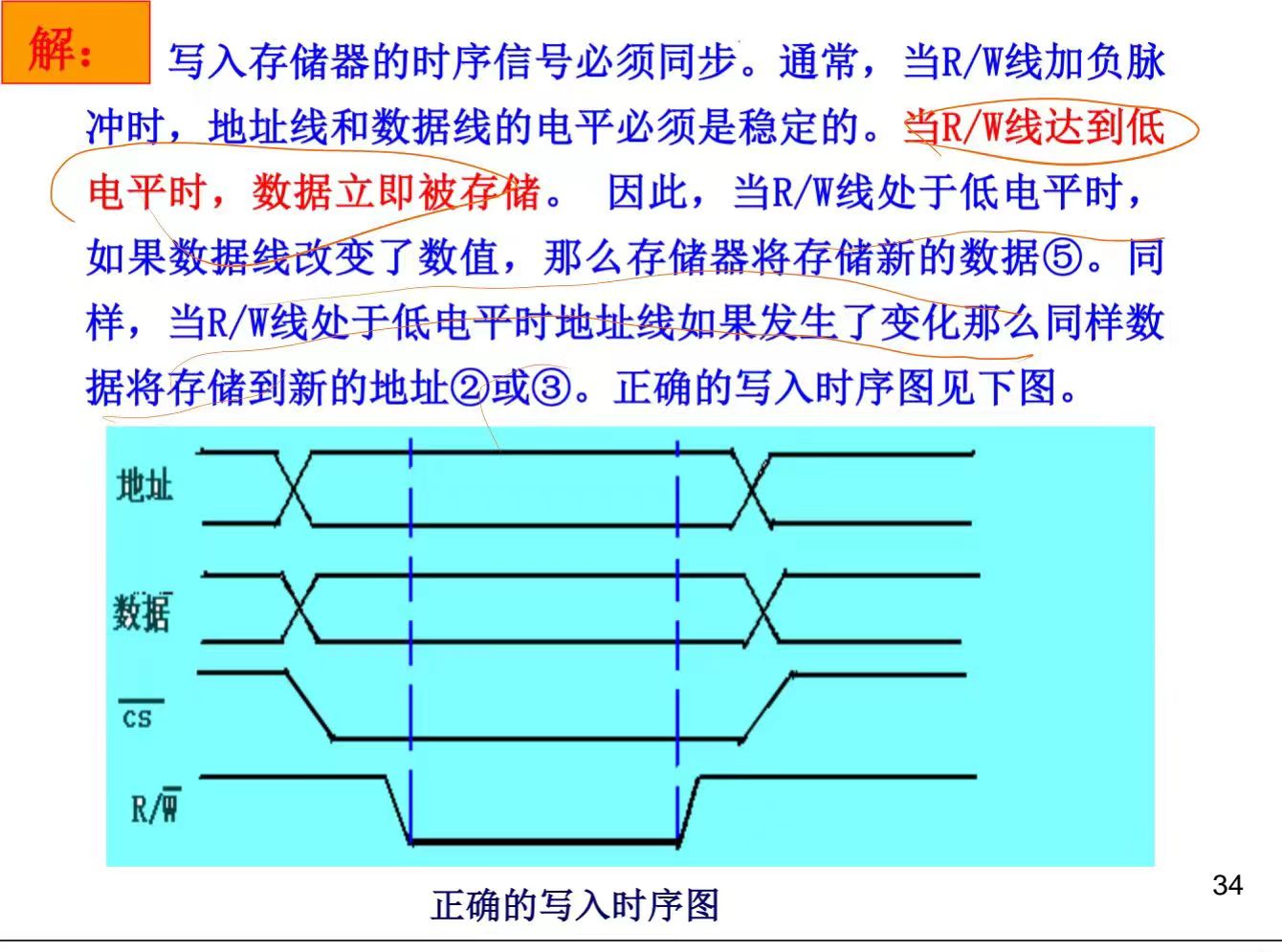

读周期与写周期的变化