定义类

I/O数据传送的控制方式(或者叫外设信息交换方式)

程序查询

- 工作过程

CPU传送数据之前先检查外设的状态,若没有准备好,则继续查询等待,直至外设就绪即进行数据传送。

- 硬件要求

只需接口电路的状态、数据口,不需增加其他控制电路。

- 特点

CPU主动查询,程序控制数据传送过程,简单易行;

每次查询之后只能传送一个字或一个字节的数据,数据传输率不高,CPU时间浪费较多。

CPU与外设之间串行传输

程序中断

- 工作过程

CPU有传送要求时,启动外设后可处理其他事件,当外设准备就绪后,通过中断方式和CPU完成数据传送工作。

- 硬件要求

需要附加的中断控制电路。

- 特点

- 一定程度上实现了CPU和外设的并行工作;

- 中断操作过程增加了软硬件的开销,且每次数据传送只能传送一个字或一个字节的数据,数据传送效率低。

DMA方式

详细内容可以参考https://aye10032.gitbook.io/computerorganizationnote/di-qi-zhang-io-xi-tong/7.4-io-fang-shi#id-7.4.3-dma-fang-shi里面关于DMA的讲解

- 工作过程

CPU分配总线使用权之后,在硬件DMA控制器(DMAC)的控制下完成存储器与高速外设之间的大量数据的传送。

- 硬件要求

需要相应的DMA控制器及数据通路,电路结构复杂,硬件开销大。

- 特点

- 数据传送不需要经过CPU,直接由硬件控制;

- 外设与存储器之间的数据传送量大。

- 一块一块的传送

- 并行传送

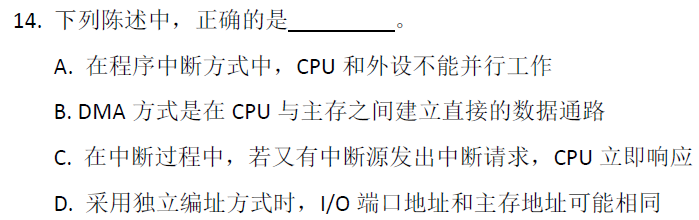

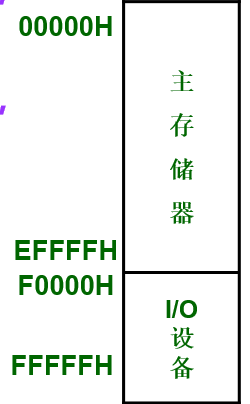

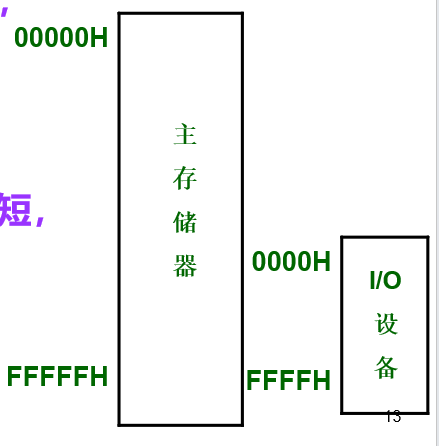

I/O端口设备编址

解析:

统一编址

将I/O系统与主存系统作为一个整体进行编址

- 优点:

访问I/O端口可使用访存指令,操作类型多样,使用灵活;

I/O端口有较大的编址空间;

- 缺点:

占用主存空间,使实际主存容量减小;

I/O访问的指令字长较长,执行速度慢

独立编址

将I/O系统与主存系统分别编址;

- 特点:

I/O端口地址不占用主存空间;

使用专用的I/O指令,指令字长短,执行速度快;

与主存空间区分容易。

中断

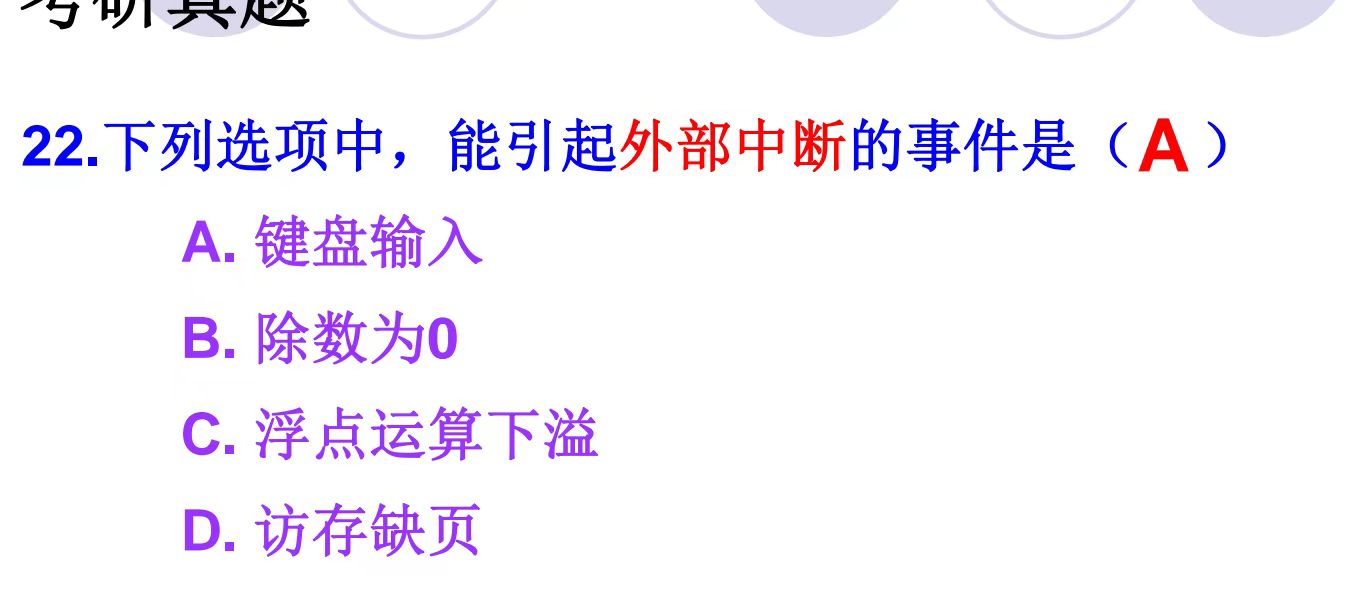

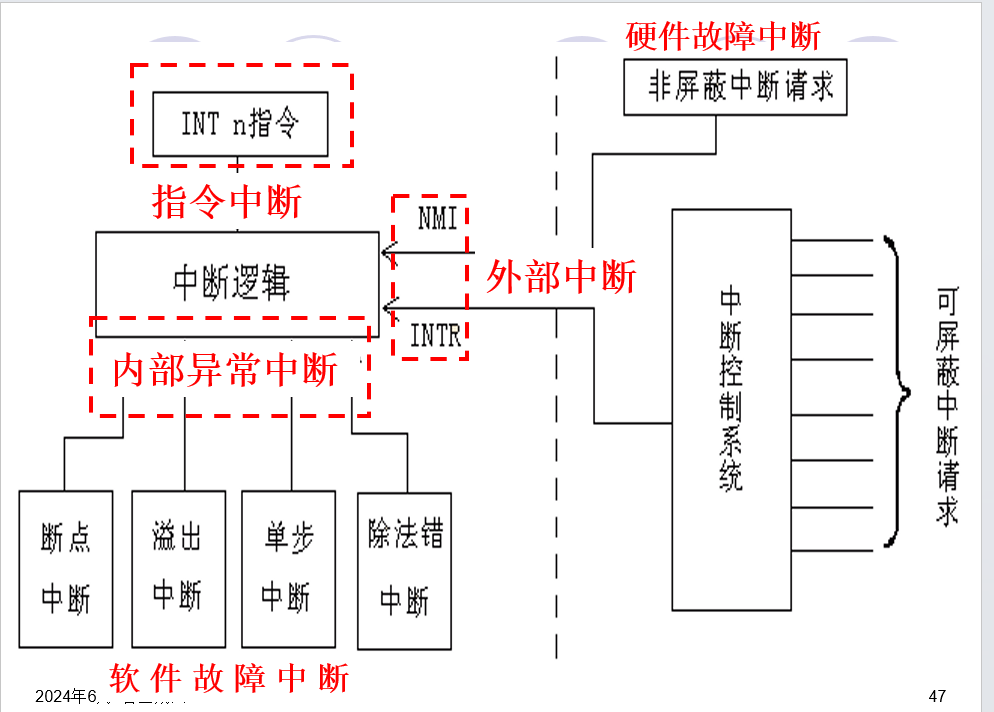

中断类型

不可屏蔽中断NMI

- 中断优先权高于可屏蔽中断INTR,一般用于系统对紧急情况的处理,用户不能使用

- 常见的NMI中断: 系统RAM奇偶校验错、I/O通道校验错、协处理器出错等。

可屏蔽中断INTR

- 此类中断的中断类型号由中断源提供;

- 外部设备的中断请求,如I/O设备的数据传送请求,用户可自行设计;

指令中断INT n

- 程序中预先安排好的中断指令

- 中断类型号的范围为5≤n≤255 ;

- 这类中断包括BIOS中断、DOS中断以及一些未定义的自由中断(可由系统扩充或根据应用需要自定义)

异常中断

- 由CPU内部的突发事件引起的中断,是不可屏蔽中断;

- CPU运行过程中的突发事件引起系统在适当位置自动添加一条中断指令,然后由CPU执行该指令引起的中断;

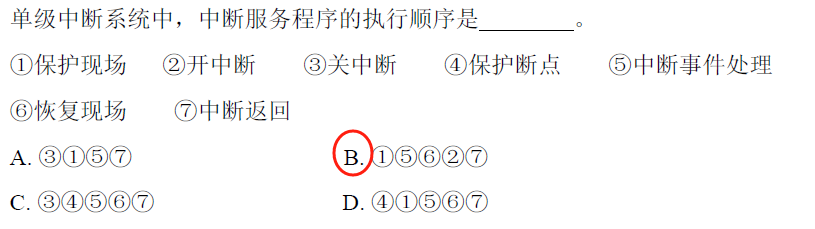

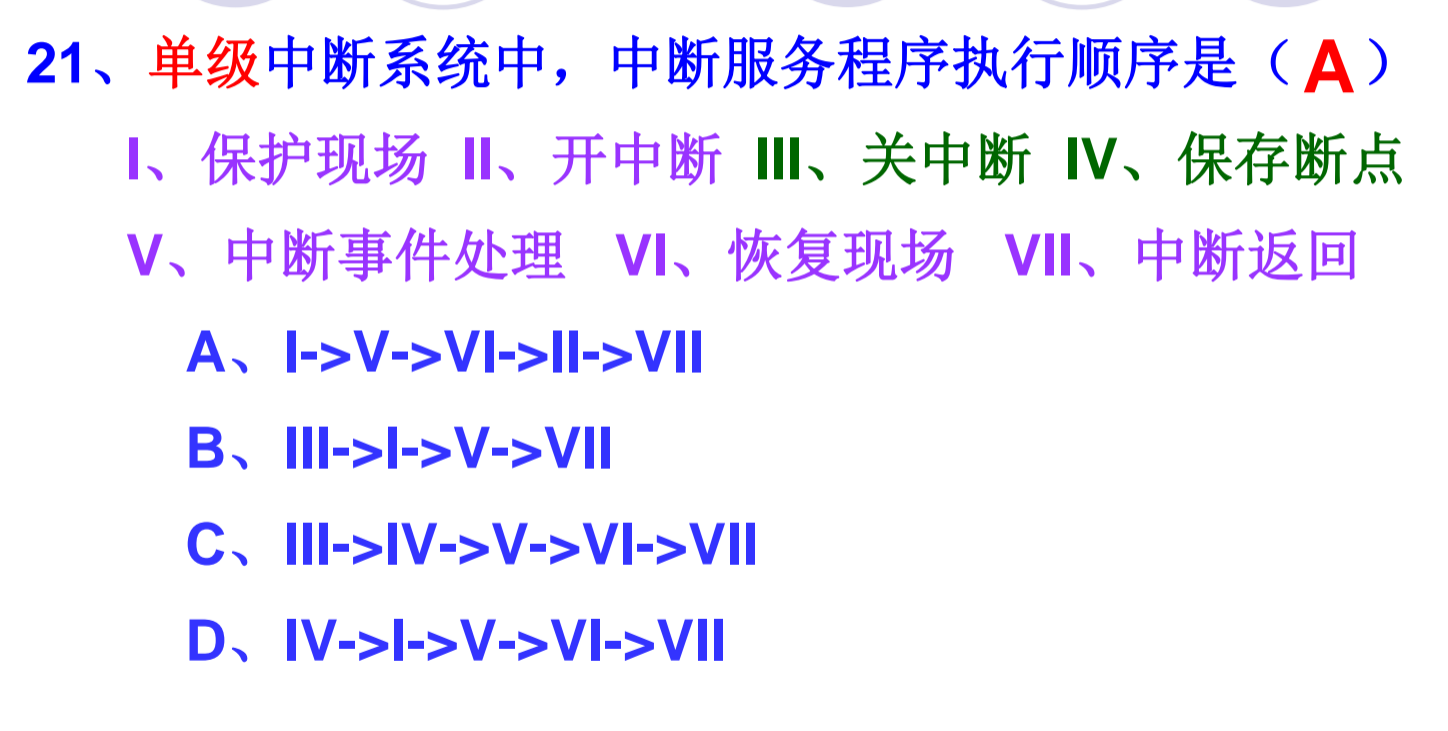

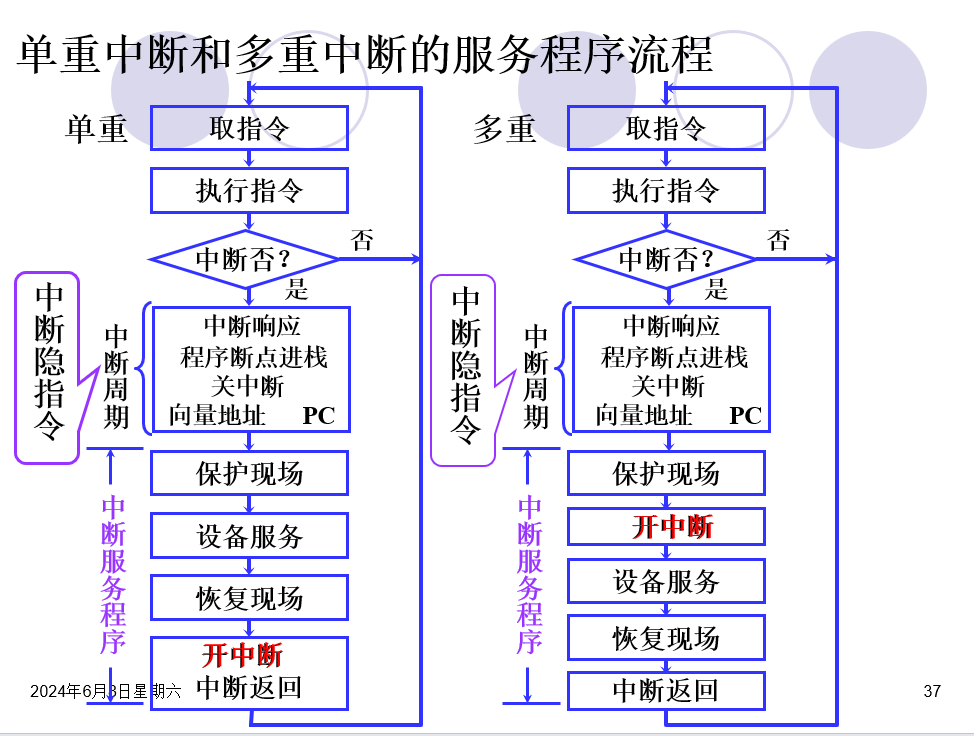

程序中断里面的中断服务程序

- 保护现场:保存通用寄存器和状态寄存器的内容

- 中断服务

- 恢复现场:通过出栈指令或取数指令把之前保存的信息送回寄存器中

- 中断返回:弹出栈顶存储的程序断点信息(原PC值),返回到原程序的断点处

- 开中断

注意中断服务程序和硬件区别,关中断和保存断点是硬件做的

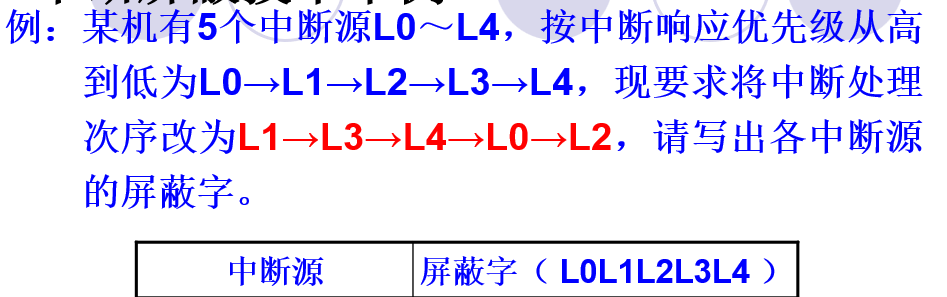

多级中断屏蔽字

置“1”(关闭)本级和低级的中断屏蔽触发器; 清“0”(开放)更高级的中断屏蔽触发器;

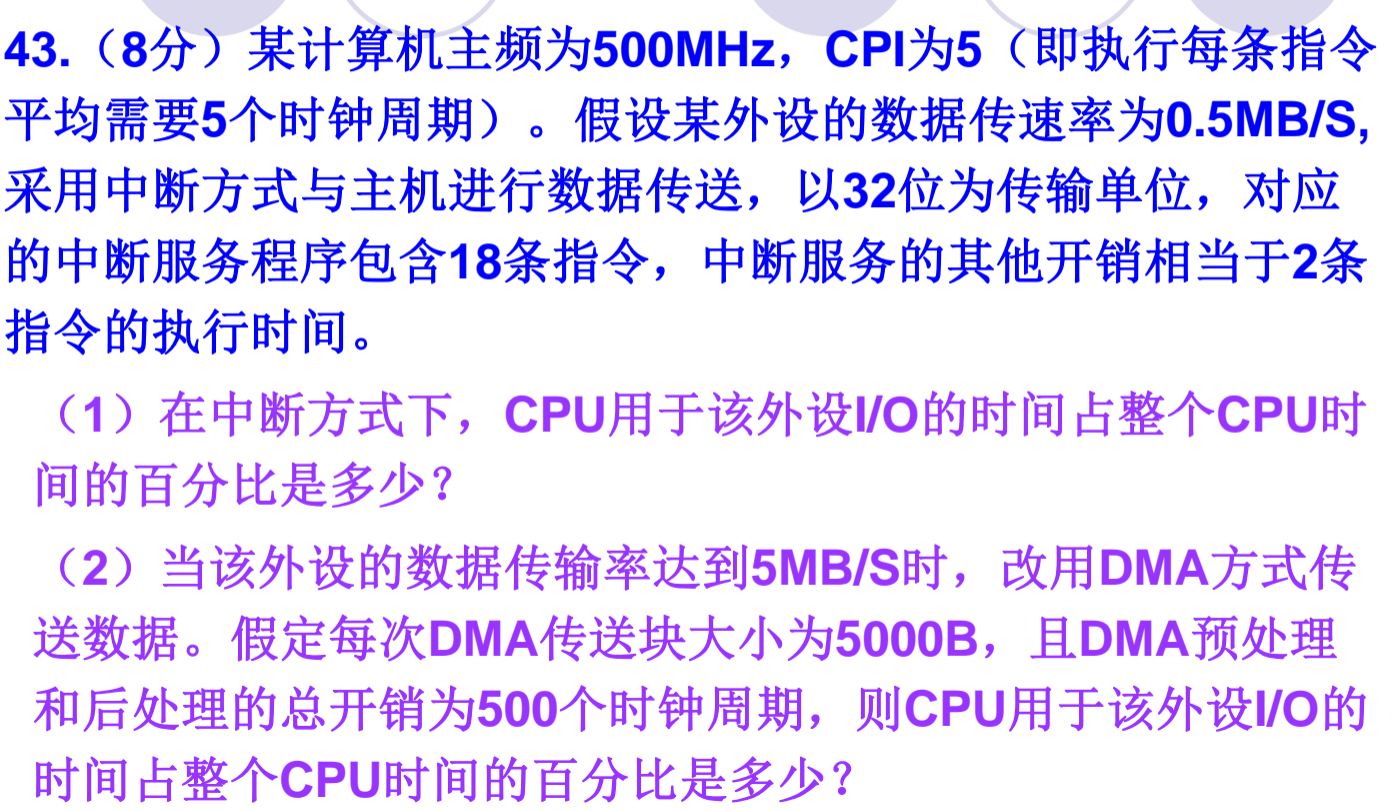

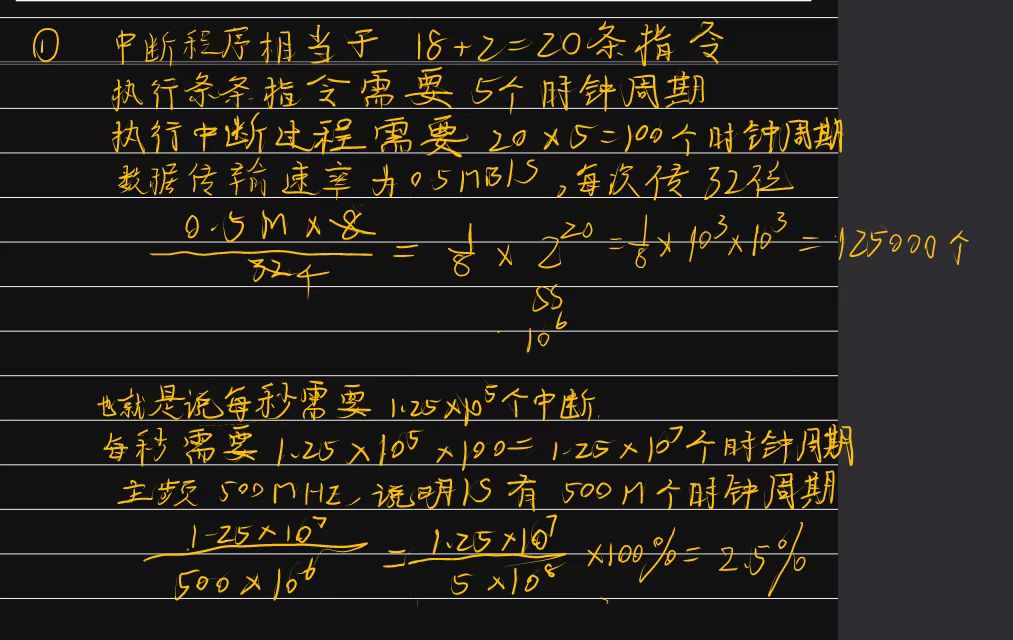

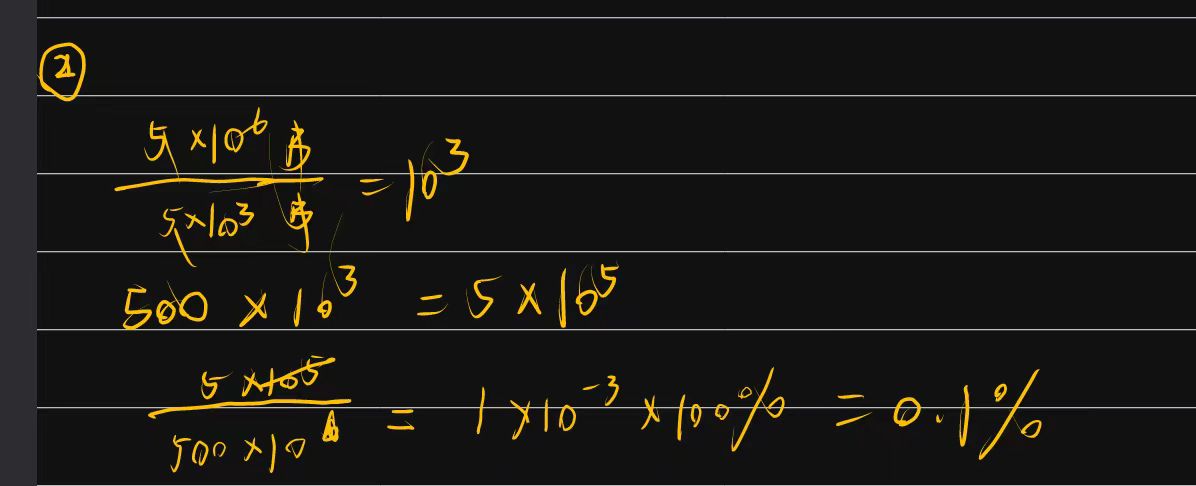

计算题

中断占CPU时间的计算

首先计算1秒钟需要多少次中断(一般根据需要传输多少数据来计算),然后根据一次中断需要多少个时钟周期计算1秒钟总共需要的时钟周期,再除以CPU主频